# **Shenzhen Haoxinsheng Technology Co., Ltd.**

# haoxinshengic.com

# DATASHEET

Whatsapp: +8615816789795

Skype: 8615816789795

WeChat: 15816789795

Viber: +8615816789795

E-mail: info@haoxinshengic.com

# **Cyclone V Device Datasheet**

ID: **683801**

CV-51002 Version: 2019.11.27

# **Contents**

| clone V Device Datasheet                                    |   |

|-------------------------------------------------------------|---|

| Electrical Characteristics                                  |   |

| Operating Conditions                                        |   |

| Switching Characteristics                                   | 2 |

| Transceiver Performance Specifications                      |   |

| Core Performance Specifications                             | 4 |

| Periphery Performance                                       | 4 |

| HPS Specifications                                          | 5 |

| Configuration Specifications                                | 6 |

| POR Specifications                                          | 6 |

| FPGA JTAG Configuration Timing                              | 6 |

| FPP Configuration Timing                                    | 6 |

| Active Serial (AS) Configuration Timing                     | 7 |

| DCLK Frequency Specification in the AS Configuration Scheme | 7 |

| Passive Serial (PS) Configuration Timing                    |   |

| Initialization                                              | 7 |

| Configuration Files                                         | 7 |

| Minimum Configuration Time Estimation                       | 7 |

| Remote System Upgrades                                      | 8 |

| User Watchdog Internal Oscillator Frequency Specifications  | 8 |

| I/O Timing                                                  | 8 |

| Programmable IOE Delay                                      | 8 |

| Programmable Output Buffer Delay                            | 8 |

| Glossary                                                    |   |

| Document Revision History for Cyclone V Device Datasheet    | 8 |

# **Cyclone V Device Datasheet**

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Cyclone® V devices.

Cyclone V devices are offered in commercial and industrial grades. Commercial devices are offered in -C6 (fastest), -C7, and -C8 speed grades. Industrial grade devices are offered in the -I7 speed grade. Automotive devices are offered in the -A7 speed grade.

Cyclone V SoC devices are also offered in a low-power variant, as indicated by the L power option in the device part number. These devices have 30% static power reduction for devices with 25K LE and 40K LE, and 20% static power reduction for devices with 85K LE and 110K LE. Note that the L power option devices are only available in –I7 speed grade, and have the equivalent operating conditions and timing specifications as the standard –I7 speed grade devices.

**Table 1.** Low Power Variants

| Density | Ordering Part Number (OPN) | Static Power Reduction |

|---------|----------------------------|------------------------|

| 25K LE  | 5CSEBA2U19I7LN             | 30%                    |

|         | 5CSEBA2U23I7LN             |                        |

|         | 5CSXFC2C6U23I7LN           |                        |

| 40K LE  | 5CSEBA4U19I7LN             |                        |

|         | 5CSEBA4U23I7LN             |                        |

|         | 5CSXFC4C6U23I7LN           |                        |

| 85K LE  | 5CSEBA5U19I7LN             | 20%                    |

|         | 5CSEBA5U23I7LN             |                        |

|         | 5CSXC5C6U23I7LN            |                        |

|         |                            | continued              |

| Density | Ordering Part Number (OPN) | Static Power Reduction |

|---------|----------------------------|------------------------|

| 110K LE | 5CSEBA6U19I7LN             |                        |

|         | 5CSEBA6U23I7LN             |                        |

|         | 5CSXFC6C6U23I7LN           |                        |

To estimate total power consumption for a low-power device, listed in Table 1 on page 3:

- 1. Multiply the Total Static Power reported by the Early Power Estimator (EPE) by the appropriate scale factor:

- For 25K LE and 40K LE devices, use 0.7

- For 85K LE and 110K LE devices, use 0.8

- 2. Add the result from Step 1 on page 4 to the Total Dynamic Power reported by the EPE.

#### **Related Information**

Cyclone V Device Overview

Provides more information about the densities and packages of devices in the Cyclone V family.

## **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Cyclone V devices.

# **Operating Conditions**

Cyclone V devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Cyclone V devices, you must consider the operating requirements described in this section.

# **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Cyclone V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms.

The functional operation of the device is not implied for these conditions.

#### Caution:

Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

**Table 2.** Absolute Maximum Ratings for Cyclone V Devices

| Symbol                         | Description                                                            | Minimum | Maximum | Unit |

|--------------------------------|------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>                | Core voltage and periphery circuitry power supply                      | -0.5    | 1.43    | V    |

| V <sub>CCPGM</sub>             | Configuration pins power supply                                        | -0.5    | 3.90    | V    |

| V <sub>CC_AUX</sub>            | Auxiliary supply                                                       | -0.5    | 3.25    | V    |

| V <sub>CCBAT</sub>             | Battery back-up power supply for design security volatile key register | -0.5    | 3.90    | V    |

| V <sub>CCPD</sub>              | I/O pre-driver power supply                                            | -0.5    | 3.90    | V    |

| V <sub>CCIO</sub>              | I/O power supply                                                       | -0.5    | 3.90    | V    |

| V <sub>CCA_FPLL</sub>          | Phase-locked loop (PLL) analog power supply                            | -0.5    | 3.25    | V    |

| V <sub>CCH_GXB</sub>           | Transceiver high voltage power                                         | -0.5    | 3.25    | V    |

| V <sub>CCE_GXB</sub>           | Transceiver power                                                      | -0.5    | 1.50    | V    |

| V <sub>CCL_GXB</sub>           | Transceiver clock network power                                        | -0.5    | 1.50    | V    |

| V <sub>I</sub>                 | DC input voltage                                                       | -0.5    | 3.80    | V    |

| V <sub>CC_HPS</sub>            | HPS core voltage and periphery circuitry power supply                  | -0.5    | 1.43    | V    |

| V <sub>CCPD_HPS</sub>          | HPS I/O pre-driver power supply                                        | -0.5    | 3.90    | V    |

| V <sub>CCIO_HPS</sub>          | HPS I/O power supply                                                   | -0.5    | 3.90    | V    |

| V <sub>CCRSTCLK_HPS</sub>      | HPS reset and clock input pins power supply                            | -0.5    | 3.90    | V    |

| V <sub>CCPLL_HPS</sub>         | HPS PLL analog power supply                                            | -0.5    | 3.25    | V    |

| V <sub>CC_AUX_SHARED</sub> (1) | HPS auxiliary power supply                                             | -0.5    | 3.25    | V    |

| I <sub>OUT</sub>               | DC output current per pin                                              | -25     | 40      | mA   |

| Т                              | Operating junction temperature                                         | -55     | 125     | °C   |

| T <sub>STG</sub>               | Storage temperature (no bias)                                          | -65     | 150     | °C   |

<sup>(1)</sup> V<sub>CC\_AUX\_SHARED</sub> must be powered by the same source as V<sub>CC\_AUX</sub> for Cyclone V SX C5, C6, D5, and D6 devices, and Cyclone V SE A5 and A6 devices.

#### **Maximum Allowed Overshoot and Undershoot Voltage**

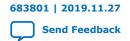

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for  $\sim 15\%$  over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

Table 3. Maximum Allowed Overshoot During Transitions for Cyclone V Devices

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

| Symbol  | Description      | Condition (V) | Overshoot Duration as % of High Time | Unit      |

|---------|------------------|---------------|--------------------------------------|-----------|

| Vi (AC) | AC input voltage | 3.8           | 100                                  | %         |

|         |                  | 3.85          | 68                                   | %         |

|         |                  | 3.9           | 45                                   | %         |

|         |                  | 3.95          | 28                                   | %         |

|         |                  | 4             | 15                                   | %         |

|         |                  | 4.05          | 13                                   | %         |

|         |                  | 4.1           | 11                                   | %         |

|         |                  | 4.15          | 9                                    | %         |

|         |                  | 4.2           | 8                                    | %         |

|         |                  | 4.25          | 7                                    | %         |

|         |                  | 4.3           | 5.4                                  | %         |

|         |                  | 4.35          | 3.2                                  | %         |

|         |                  | 4.4           | 1.9                                  | %         |

|         |                  | 4.45          | 1.1                                  | %         |

|         | •                |               | •                                    | continued |

| Symbol | Description | Condition (V) Overshoot Duration as % of High Time |     | Unit |

|--------|-------------|----------------------------------------------------|-----|------|

|        |             | 4.5                                                | 0.6 | %    |

|        |             | 4.55                                               | 0.4 | %    |

|        |             | 4.6                                                | 0.2 | %    |

For an overshoot of 3.8 V, the percentage of high time for the overshoot can be as high as 100% over a 10-year period. Percentage of high time is calculated as ([delta T]/T)  $\times$  100. This 10-year period assumes that the device is always turned on with 100% I/O toggle rate and 50% duty cycle signal.

Figure 1. Cyclone V Devices Overshoot Duration

# **Recommended Operating Conditions**

This section lists the functional operation limits for the AC and DC parameters for Cyclone V devices.

#### **Recommended Operating Conditions**

#### Table 4. Recommended Operating Conditions for Cyclone V Devices

This table lists the steady-state voltage values expected from Cyclone V devices. Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol                           | Description                                                                                | Condition                                                    | Minimum <sup>(2)</sup> | Typical | Maximum <sup>(2)</sup> | Unit      |

|----------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------|---------|------------------------|-----------|

| tra                              | Core voltage, periphery circuitry power supply, transceiver physical coding sublayer (PCS) | Devices without internal scrubbing feature                   | 1.07                   | 1.1     | 1.13                   | V         |

|                                  | power supply, and transceiver PCI Express* (PCIe*) hard IP digital power supply            | Devices with internal scrubbing feature (with SC suffix) (3) | 1.12                   | 1.15    | 1.18                   | V         |

| V <sub>CC_AUX</sub>              | Auxiliary supply                                                                           | _                                                            | 2.375                  | 2.5     | 2.625                  | V         |

| V <sub>CCPD</sub> <sup>(4)</sup> | I/O pre-driver power supply                                                                | 3.3 V                                                        | 3.135                  | 3.3     | 3.465                  | V         |

|                                  |                                                                                            | 3.0 V                                                        | 2.85                   | 3.0     | 3.15                   | V         |

|                                  |                                                                                            | 2.5 V                                                        | 2.375                  | 2.5     | 2.625                  | V         |

| V <sub>CCIO</sub>                | I/O buffers power supply                                                                   | 3.3 V                                                        | 3.135                  | 3.3     | 3.465                  | V         |

|                                  |                                                                                            | 3.0 V                                                        | 2.85                   | 3.0     | 3.15                   | V         |

|                                  |                                                                                            | 2.5 V                                                        | 2.375                  | 2.5     | 2.625                  | V         |

|                                  |                                                                                            | 1.8 V                                                        | 1.71                   | 1.8     | 1.89                   | V         |

|                                  |                                                                                            | 1.5 V                                                        | 1.425                  | 1.5     | 1.575                  | V         |

|                                  |                                                                                            | 1.35 V                                                       | 1.283                  | 1.35    | 1.418                  | V         |

|                                  |                                                                                            | 1.25 V                                                       | 1.19                   | 1.25    | 1.31                   | V         |

|                                  |                                                                                            | 1.2 V                                                        | 1.14                   | 1.2     | 1.26                   | V         |

|                                  | ·                                                                                          | •                                                            |                        |         | •                      | continued |

<sup>(2)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(3)</sup> The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

<sup>(4)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.  $V_{CCPD}$  must be 3.3 V when  $V_{CCIO}$  is 3.3 V.

| Symbol                               | Description                                                              | Condition    | Minimum <sup>(2)</sup> | Typical | Maximum <sup>(2)</sup> | Unit |

|--------------------------------------|--------------------------------------------------------------------------|--------------|------------------------|---------|------------------------|------|

| V <sub>CCPGM</sub>                   | Configuration pins power supply                                          | 3.3 V        | 3.135                  | 3.3     | 3.465                  | V    |

|                                      |                                                                          | 3.0 V        | 2.85                   | 3.0     | 3.15                   | V    |

|                                      |                                                                          | 2.5 V        | 2.375                  | 2.5     | 2.625                  | V    |

|                                      |                                                                          | 1.8 V        | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CCA_FPLL</sub> <sup>(5)</sup> | PLL analog voltage regulator power supply                                | _            | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCBAT</sub> <sup>(6)</sup>    | Battery back-up power supply (For design security volatile key register) | -            | 1.2                    | _       | 3.0                    | V    |

| V <sub>I</sub>                       | DC input voltage                                                         | _            | -0.5                   | _       | 3.6                    | V    |

| Vo                                   | Output voltage                                                           | _            | 0                      | _       | V <sub>CCIO</sub>      | V    |

| Тյ                                   | Operating junction temperature                                           | Commercial   | 0                      | _       | 85                     | °C   |

|                                      |                                                                          | Industrial   | -40                    | _       | 100                    | °C   |

|                                      |                                                                          | Automotive   | -40                    | _       | 125                    | °C   |

| t <sub>RAMP</sub> <sup>(7)</sup>     | Power supply ramp time                                                   | Standard POR | 200µs                  | _       | 100ms                  | _    |

|                                      |                                                                          | Fast POR     | 200µs                  | _       | 4ms                    | _    |

<sup>(2)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(5)</sup> PLL digital voltage is regulated from V<sub>CCA FPLL</sub>.

<sup>(6)</sup> If you do not use the design security feature in Cyclone V devices, connect  $V_{CCBAT}$  to a 1.5-V, 2.5-V, or 3.0-V power supply. Cyclone V power-on reset (POR) circuitry monitors  $V_{CCBAT}$ . Cyclone V devices do not exit POR if  $V_{CCBAT}$  is not powered up.

This is also applicable to HPS power supply. For HPS power supply, refer to  $t_{RAMP}$  specifications for standard POR when HPS\_PORSEL = 0 and  $t_{RAMP}$  specifications for fast POR when HPS PORSEL = 1.

#### **Transceiver Power Supply Operating Conditions**

#### Table 5. Transceiver Power Supply Operating Conditions for Cyclone V GX, GT, SX, and ST Devices

| Symbol                        | Description                                | Minimum <sup>(8)</sup> | Typical | Maximum <sup>(8)</sup> | Unit |

|-------------------------------|--------------------------------------------|------------------------|---------|------------------------|------|

| V <sub>CCH_GXBL</sub>         | Transceiver high voltage power (left side) | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCE_GXBL</sub> (9)(10) | Transmitter and receiver power (left side) | 1.07/1.17              | 1.1/1.2 | 1.13/1.23              | V    |

| V <sub>CCL_GXBL</sub> (9)(10) | Clock network power (left side)            | 1.07/1.17              | 1.1/1.2 | 1.13/1.23              | V    |

#### **Related Information**

PCIe Supported Configurations and Placement Guidelines

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices which require full compliance to the PCIe Gen2 transmit jitter specification.

• 6.144-Gbps Support Capability in Cyclone V GT Devices

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices for CPRI 6.144 Gbps.

<sup>(10)</sup> Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for full compliance to CPRI transmit jitter specification at 4.9152 Gbps (Cyclone V GT and ST devices) and 6.144Gbps (Cyclone V GT and ST devices only). For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices for CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

<sup>(8)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(9)</sup> Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which require full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

#### **HPS Power Supply Operating Conditions**

#### Table 6. HPS Power Supply Operating Conditions for Cyclone V SX and ST Devices

This table lists the steady-state voltage and current values expected from Cyclone V system-on-a-chip (SoC) devices with Arm\*-based hard processor system (HPS). Power supply ramps must all be strictly monotonic, without plateaus. Refer to the *Recommended Operating Conditions for Cyclone V Devices* table for the steady-state voltage values expected from the FPGA portion of the Cyclone V SoC devices.

| Symbol                     | Description                                           | Condition              | Minimum <sup>(11)</sup> | Typical | Maximum <sup>(11)</sup> | Unit      |

|----------------------------|-------------------------------------------------------|------------------------|-------------------------|---------|-------------------------|-----------|

| V <sub>CC_HPS</sub>        | HPS core voltage and periphery circuitry power supply | -                      | 1.07                    | 1.1     | 1.13                    | V         |

| V <sub>CCPD_HPS</sub> (12) | HPS I/O pre-driver power supply                       | 3.3 V                  | 3.135                   | 3.3     | 3.465                   | V         |

|                            | 3.0 V                                                 | 2.85                   | 3.0                     | 3.15    | V                       |           |

|                            |                                                       | 2.5 V                  | 2.375                   | 2.5     | 2.625                   | V         |

| V <sub>CCIO_HPS</sub>      | HPS I/O buffers power supply                          | 3.3 V                  | 3.135                   | 3.3     | 3.465                   | V         |

|                            |                                                       | 3.0 V                  | 2.85                    | 3.0     | 3.15                    | V         |

|                            |                                                       | 2.5 V                  | 2.375                   | 2.5     | 2.625                   | V         |

|                            |                                                       | 1.8 V                  | 1.71                    | 1.8     | 1.89                    | V         |

|                            |                                                       | 1.5 V                  | 1.425                   | 1.5     | 1.575                   | V         |

|                            |                                                       | 1.35 V <sup>(13)</sup> | 1.283                   | 1.35    | 1.418                   | V         |

|                            |                                                       | 1.2 V                  | 1.14                    | 1.2     | 1.26                    | V         |

| V <sub>CCRSTCLK_HPS</sub>  | HPS reset and clock input pins power supply           | 3.3 V                  | 3.135                   | 3.3     | 3.465                   | V         |

|                            |                                                       | 3.0 V                  | 2.85                    | 3.0     | 3.15                    | V         |

|                            |                                                       | 2.5 V                  | 2.375                   | 2.5     | 2.625                   | V         |

|                            |                                                       |                        |                         |         |                         | continued |

<sup>(11)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

$<sup>^{(13)}</sup>$   $\,V_{CCIO\_HPS}$  1.35 V is supported for HPS row I/O bank only.

$<sup>^{(12)}</sup>$  V<sub>CCPD\_HPS</sub> must be 2.5 V when V<sub>CCIO\_HPS</sub> is 2.5, 1.8, 1.5, or 1.2 V. V<sub>CCPD\_HPS</sub> must be 3.0 V when V<sub>CCIO\_HPS</sub> is 3.0 V. V<sub>CCPD\_HPS</sub> must be 3.3 V when V<sub>CCIO\_HPS</sub> is 3.3 V.

| Symbol                          | Description                                   | Condition | Minimum <sup>(11)</sup> | Typical | Maximum <sup>(11)</sup> | Unit |

|---------------------------------|-----------------------------------------------|-----------|-------------------------|---------|-------------------------|------|

|                                 |                                               | 1.8 V     | 1.71                    | 1.8     | 1.89                    | V    |

| V <sub>CCPLL_HPS</sub>          | HPS PLL analog voltage regulator power supply | _         | 2.375                   | 2.5     | 2.625                   | V    |

| V <sub>CC_AUX_SHARED</sub> (14) | HPS auxiliary power supply                    | _         | 2.375                   | 2.5     | 2.625                   | V    |

#### **Related Information**

Recommended Operating Conditions on page 8

Provides the steady-state voltage values for the FPGA portion of the device.

#### **DC Characteristics**

#### **Supply Current and Power Consumption**

Intel offers two ways to estimate power for your design—the Excel-based Early Power Estimator (EPE) and the Intel® Quartus® Prime Power Analyzer feature.

Use the Excel-based EPE before you start your design to estimate the supply current for your design. The EPE provides a magnitude estimate of the device power because these currents vary greatly with the resources you use.

The Intel Quartus Prime Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- Early Power Estimator User Guide

Provides more information about power estimation tools.

- Power Analysis chapter, Intel Quartus Prime Handbook

Provides more information about power estimation tools.

<sup>(14)</sup> V<sub>CC\_AUX\_SHARED</sub> must be powered by the same source as V<sub>CC\_AUX</sub> for Cyclone V SX C5, C6, D5, and D6 devices, and Cyclone V SE A5 and A6 devices.

<sup>(11)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

## I/O Pin Leakage Current

Table 7. I/O Pin Leakage Current for Cyclone V Devices

| Symbol          | Description        | Condition                                    | Min | Тур | Max | Unit |

|-----------------|--------------------|----------------------------------------------|-----|-----|-----|------|

| II              | Input pin          | $V_{\rm I} = 0 \text{ V to V}_{\rm CCIOMAX}$ | -30 | _   | 30  | μА   |

| I <sub>OZ</sub> | Tri-stated I/O pin | V <sub>O</sub> = 0 V to V <sub>CCIOMAX</sub> | -30 | _   | 30  | μА   |

#### **Bus Hold Specifications**

## **Table 8.** Bus Hold Parameters for Cyclone V Devices

The bus-hold trip points are based on calculated input voltages from the JEDEC\* standard.

| Parameter                                | Symbol            | Condition                                  |     |      |       |       |      | V <sub>CCI</sub> | , (V) |      |     |      |     |      | Unit |

|------------------------------------------|-------------------|--------------------------------------------|-----|------|-------|-------|------|------------------|-------|------|-----|------|-----|------|------|

|                                          |                   |                                            | 1.  | .2   | 1.    | .5    | 1.   | 8                | 2.    | 5    | 3.  | .0   | 3.  | .3   |      |

|                                          |                   |                                            | Min | Max  | Min   | Max   | Min  | Max              | Min   | Max  | Min | Max  | Min | Max  |      |

| Bus-hold, low,<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub> (max)    | 8   | _    | 12    | _     | 30   | _                | 50    | _    | 70  | _    | 70  | _    | μА   |

| Bus-hold, high,<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(min) | -8  | _    | -12   | _     | -30  | _                | -50   | _    | -70 | _    | -70 | _    | μА   |

| Bus-hold, low, overdrive current         | I <sub>ODL</sub>  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>  | _   | 125  | _     | 175   | _    | 200              | _     | 300  | _   | 500  | _   | 500  | μА   |

| Bus-hold, high, overdrive current        | I <sub>ODH</sub>  | 0 V <v<sub>IN <v<sub>CCIO</v<sub></v<sub>  | _   | -125 | _     | -175  | _    | -200             | _     | -300 | _   | -500 | _   | -500 | μА   |

| Bus-hold trip<br>point                   | V <sub>TRIP</sub> | _                                          | 0.3 | 0.9  | 0.375 | 1.125 | 0.68 | 1.07             | 0.7   | 1.7  | 0.8 | 2    | 0.8 | 2    | V    |

#### **OCT Calibration Accuracy Specifications**

If you enable on-chip termination (OCT) calibration, calibration is automatically performed at power up for I/Os connected to the calibration block.

# Table 9. OCT Calibration Accuracy Specifications for Cyclone V Devices

Calibration accuracy for the calibrated on-chip series termination ( $R_S$  OCT) and on-chip parallel termination ( $R_T$  OCT) are applicable at the moment of calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.

| Symbol                                        | Description                                                                                                                            | Condition (V)                               | Ca         | alibration Accura | су         | Unit |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-------------------|------------|------|

|                                               |                                                                                                                                        |                                             | -C6        | -I7, -C7          | -C8, -A7   |      |

| 25-Ω R <sub>S</sub>                           | Internal series termination with calibration (25- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>S</sub>                           | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 34- $\Omega$ and 40- $\Omega$ R <sub>S</sub>  | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2    | ±15        | ±15               | ±15        | %    |

| 48-Ω, 60-Ω, and 80-Ω $R_S$                    | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , and 80- $\Omega$ setting)                                  | V <sub>CCIO</sub> = 1.2                     | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>T</sub>                           | Internal parallel termination with calibration (50- $\Omega$ setting)                                                                  | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2      | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 20-Ω, 30-Ω, 40-Ω,60-Ω, and 120-Ω $R_T$        | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25         | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 60- $\Omega$ and 120- $\Omega$ R <sub>T</sub> | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | V <sub>CCIO</sub> = 1.2                     | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 25-Ω R <sub>S_left_shift</sub>                | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                               | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

#### **OCT Without Calibration Resistance Tolerance Specifications**

#### Table 10. OCT Without Calibration Resistance Tolerance Specifications for Cyclone V Devices

This table lists the Cyclone V OCT without calibration resistance tolerance to PVT changes.

| Symbol               | Description                                                            | Condition (V)                | Re  | sistance Tolerar | nce      | Unit |

|----------------------|------------------------------------------------------------------------|------------------------------|-----|------------------|----------|------|

|                      |                                                                        |                              | -C6 | -I7, -C7         | -C8, -A7 |      |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0, 2.5 | ±30 | ±40              | ±40      | %    |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8, 1.5 | ±30 | ±40              | ±40      | %    |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2      | ±35 | ±50              | ±50      | %    |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0, 2.5 | ±30 | ±40              | ±40      | %    |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8, 1.5 | ±30 | ±40              | ±40      | %    |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2      | ±35 | ±50              | ±50      | %    |

| 100-Ω R <sub>D</sub> | Internal differential termination (100- $\Omega$ setting)              | V <sub>CCIO</sub> = 2.5      | ±25 | ±40              | ±40      | %    |

### Figure 2. Equation for OCT Variation Without Recalibration

$$R_{OCT} = R_{SCAL} \left( 1 + \left| \frac{dR}{dT} \times \Delta T \right| \pm \left| \frac{dR}{dV} \times \Delta V \right| \right)$$

The definitions for the equation are as follows:

- The R<sub>OCT</sub> value calculated shows the range of OCT resistance with the variation of temperature and V<sub>CCIO</sub>.

- R<sub>SCAL</sub> is the OCT resistance value at power-up.

- $\bullet\quad \Delta T$  is the variation of temperature with respect to the temperature at power up.

- $\Delta V$  is the variation of voltage with respect to the  $V_{CCIO}$  at power up.

- dR/dT is the percentage change of R<sub>SCAL</sub> with temperature.

- $\bullet$  dR/dV is the percentage change of R<sub>SCAL</sub> with voltage.

### **OCT Variation after Power-Up Calibration**

#### Table 11. OCT Variation after Power-Up Calibration for Cyclone V Devices

This table lists OCT variation with temperature and voltage after power-up calibration. The OCT variation is valid for a  $V_{\text{CCIO}}$  range of  $\pm 5\%$  and a temperature range of  $0^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

| Symbol | Description                                          | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|------------------------------------------------------|-----------------------|-------|------|

| dR/dV  | OCT variation with voltage without recalibration     | 3.0                   | 0.100 | %/mV |

|        |                                                      | 2.5                   | 0.100 |      |

|        |                                                      | 1.8                   | 0.100 |      |

|        |                                                      | 1.5                   | 0.100 |      |

|        |                                                      | 1.35                  | 0.150 |      |

|        |                                                      | 1.25                  | 0.150 |      |

|        |                                                      | 1.2                   | 0.150 |      |

| dR/dT  | OCT variation with temperature without recalibration | 3.0                   | 0.189 | %/°C |

|        |                                                      | 2.5                   | 0.208 |      |

|        |                                                      | 1.8                   | 0.266 |      |

|        |                                                      | 1.5                   | 0.273 |      |

|        |                                                      | 1.35                  | 0.200 |      |

|        |                                                      | 1.25                  | 0.200 |      |

|        |                                                      | 1.2                   | 0.317 |      |

# **Pin Capacitance**

**Table 12.** Pin Capacitance for Cyclone V Devices

| Symbol             | Description                                                      | Maximum | Unit |

|--------------------|------------------------------------------------------------------|---------|------|

| C <sub>IOTB</sub>  | Input capacitance on top and bottom I/O pins                     | 6       | pF   |

| C <sub>IOLR</sub>  | Input capacitance on left and right I/O pins                     | 6       | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

# **Hot Socketing**

**Table 13.** Hot Socketing Specifications for Cyclone V Devices

| Symbol                    | Description                                     | Maximum           | Unit |

|---------------------------|-------------------------------------------------|-------------------|------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                          | 300               | μΑ   |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                          | 8 <sup>(15)</sup> | mA   |

| I <sub>XCVR-TX</sub> (DC) | DC current per transceiver transmitter (TX) pin | 100               | mA   |

| I <sub>XCVR-RX</sub> (DC) | DC current per transceiver receiver (RX) pin    | 50                | mA   |

## **Internal Weak Pull-Up Resistor**

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

<sup>(15)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

Table 14. Internal Weak Pull-Up Resistor Values for Cyclone V Devices

| Symbol          | Description                                                                    | Condition (V) <sup>(16)</sup> | Value <sup>(17)</sup> | Unit |

|-----------------|--------------------------------------------------------------------------------|-------------------------------|-----------------------|------|

| R <sub>PU</sub> | Value of the I/O pin pull-up resistor before and during configuration, as well | V <sub>CCIO</sub> = 3.3 ±5%   | 25                    | kΩ   |

|                 | as user mode if you have enabled the programmable pull-up resistor option.     | V <sub>CCIO</sub> = 3.0 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 2.5 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.8 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.5 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.35 ±5%  | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.25 ±5%  | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.2 ±5%   | 25                    | kΩ   |

#### **Related Information**

Cyclone V Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

# **I/O Standard Specifications**

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Cyclone V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

$<sup>^{(16)}</sup>$  Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{\text{CCIO}}$ .

$<sup>^{(17)}</sup>$  Valid with  $\pm 10\%$  tolerances to cover changes over PVT.

#### **Single-Ended I/O Standards**

Table 15. Single-Ended I/O Standards for Cyclone V Devices

| I/O Standard |       | V <sub>CCIO</sub> (V) |       | \    | / <sub>IL</sub> (V)      | V <sub>IH</sub>          | (V)                     | V <sub>OL</sub> (V)      | V <sub>OH</sub> (V)      | I <sub>OL</sub> (18) | I <sub>OH</sub> <sup>(18)</sup> |

|--------------|-------|-----------------------|-------|------|--------------------------|--------------------------|-------------------------|--------------------------|--------------------------|----------------------|---------------------------------|

|              | Min   | Тур                   | Max   | Min  | Max                      | Min                      | Max                     | Max                      | Min                      | (mA)                 | (mA)                            |

| 3.3-V LVTTL  | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.45                     | 2.4                      | 4                    | -4                              |

| 3.3-V LVCMOS | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.2                      | V <sub>CCIO</sub> - 0.2  | 2                    | -2                              |

| 3.0-V LVTTL  | 2.85  | 3                     | 3.15  | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.4                      | 2.4                      | 2                    | -2                              |

| 3.0-V LVCMOS | 2.85  | 3                     | 3.15  | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.2                      | V <sub>CCIO</sub> - 0.2  | 0.1                  | -0.1                            |

| 3.0-V PCI*   | 2.85  | 3                     | 3.15  | _    | 0.3 × V <sub>CCIO</sub>  | 0.5 × V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3 | 0.1 × V <sub>CCIO</sub>  | 0.9 × V <sub>CCIO</sub>  | 1.5                  | -0.5                            |

| 3.0-V PCI-X  | 2.85  | 3                     | 3.15  | _    | 0.35 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3 | 0.1 × V <sub>CCIO</sub>  | 0.9 × V <sub>CCIO</sub>  | 1.5                  | -0.5                            |

| 2.5 V        | 2.375 | 2.5                   | 2.625 | -0.3 | 0.7                      | 1.7                      | 3.6                     | 0.4                      | 2                        | 1                    | -1                              |

| 1.8 V        | 1.71  | 1.8                   | 1.89  | -0.3 | 0.35 × V <sub>CCIO</sub> | 0.65 × V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.45                     | V <sub>CCIO</sub> - 0.45 | 2                    | -2                              |

| 1.5 V        | 1.425 | 1.5                   | 1.575 | -0.3 | 0.35 × V <sub>CCIO</sub> | 0.65 × V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 × V <sub>CCIO</sub> | 0.75 × V <sub>CCIO</sub> | 2                    | -2                              |

| 1.2 V        | 1.14  | 1.2                   | 1.26  | -0.3 | 0.35 × V <sub>CCIO</sub> | 0.65 × V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 × V <sub>CCIO</sub> | 0.75 × V <sub>CCIO</sub> | 2                    | -2                              |

#### Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications

Table 16. Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Cyclone V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       |                          | V <sub>REF</sub> (V)    |                          | V <sub>TT</sub> (V)     |                  |                         |  |

|------------------------|-------|-----------------------|-------|--------------------------|-------------------------|--------------------------|-------------------------|------------------|-------------------------|--|

|                        | Min   | Тур                   | Max   | Min                      | Тур                     | Max                      | Min                     | Тур              | Max                     |  |

| SSTL-2 Class I,<br>II  | 2.375 | 2.5                   | 2.625 | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 |  |

| SSTL-18 Class I,<br>II | 1.71  | 1.8                   | 1.89  | 0.833                    | 0.9                     | 0.969                    | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 |  |

|                        |       | '                     | •     |                          |                         |                          |                         |                  | continued               |  |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       |                          | V <sub>REF</sub> (V)    |                          |                          | V <sub>TT</sub> (V)     |                          |

|-------------------------|-------|-----------------------|-------|--------------------------|-------------------------|--------------------------|--------------------------|-------------------------|--------------------------|

|                         | Min   | Тур                   | Max   | Min                      | Тур                     | Max                      | Min                      | Тур                     | Max                      |

| SSTL-15 Class I,<br>II  | 1.425 | 1.5                   | 1.575 | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> |

| SSTL-135 Class<br>I, II | 1.283 | 1.35                  | 1.418 | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> |

| SSTL-125 Class<br>I, II | 1.19  | 1.25                  | 1.26  | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> |

| HSTL-18 Class I,<br>II  | 1.71  | 1.8                   | 1.89  | 0.85                     | 0.9                     | 0.95                     | _                        | V <sub>CCIO</sub> /2    | _                        |

| HSTL-15 Class I,<br>II  | 1.425 | 1.5                   | 1.575 | 0.68                     | 0.75                    | 0.9                      | _                        | V <sub>CCIO</sub> /2    | _                        |

| HSTL-12 Class I,<br>II  | 1.14  | 1.2                   | 1.26  | 0.47 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.53 × V <sub>CCIO</sub> | _                        | V <sub>CCIO</sub> /2    | _                        |

| HSUL-12                 | 1.14  | 1.2                   | 1.3   | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> | -                        | -                       | _                        |

#### Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications

Table 17. Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Cyclone V Devices

| I/O Standard        | V <sub>IL</sub> | (DC) (V)                 | V <sub>IH(DC</sub>       | c) (V)                  | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)     | V <sub>OH</sub> (V)      | I <sub>OL</sub> <sup>(19)</sup> | I <sub>OH</sub> <sup>(19)</sup> |

|---------------------|-----------------|--------------------------|--------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|---------------------------------|---------------------------------|

|                     | Min             | Max                      | Min                      | Max                     | Max                     | Min                     | Max                     | Min                      | (mA)                            | (mA)                            |

| SSTL-2 Class I      | -0.3            | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> - 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> - 0.608 | V <sub>TT</sub> + 0.608  | 8.1                             | -8.1                            |

| SSTL-2 Class<br>II  | -0.3            | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> - 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> - 0.81  | V <sub>TT</sub> + 0.81   | 16.2                            | -16.2                           |

| SSTL-18 Class<br>I  | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> - 0.25 | V <sub>REF</sub> + 0.25 | V <sub>TT</sub> - 0.603 | V <sub>TT</sub> + 0.603  | 6.7                             | -6.7                            |

| SSTL-18 Class<br>II | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> - 0.25 | V <sub>REF</sub> + 0.25 | 0.28                    | V <sub>CCIO</sub> - 0.28 | 13.4                            | -13.4                           |

|                     |                 |                          |                          |                         |                         |                         |                         |                          | CO                              | ntinued                         |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

| I/O Standard        | V <sub>IL</sub> | <sub>(DC)</sub> (V)     | V <sub>IH(DO</sub>      | c) (V)                   | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)      | V <sub>OH</sub> (V)      | I <sub>OL</sub> <sup>(19)</sup> | I <sub>OH</sub> <sup>(19)</sup> |

|---------------------|-----------------|-------------------------|-------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|---------------------------------|---------------------------------|

|                     | Min             | Max                     | Min                     | Max                      | Max                      | Min                      | Max                      | Min                      | (mA)                            | (mA)                            |

| SSTL-15 Class<br>I  | _               | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.175 | V <sub>REF</sub> + 0.175 | 0.2 × V <sub>CCIO</sub>  | 0.8 × V <sub>CCIO</sub>  | 8                               | -8                              |

| SSTL-15 Class<br>II | _               | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.175 | V <sub>REF</sub> + 0.175 | 0.2 × V <sub>CCIO</sub>  | 0.8 × V <sub>CCIO</sub>  | 16                              | -16                             |

| SSTL-135            | _               | V <sub>REF</sub> - 0.09 | V <sub>REF</sub> + 0.09 | _                        | V <sub>REF</sub> - 0.16  | V <sub>REF</sub> + 0.16  | 0.2 × V <sub>CCIO</sub>  | 0.8 × V <sub>CCIO</sub>  | _                               | _                               |

| SSTL-125            | _               | V <sub>REF</sub> - 0.85 | V <sub>REF</sub> + 0.85 | _                        | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | 0.2 × V <sub>CCIO</sub>  | 0.8 × V <sub>CCIO</sub>  | _                               | _                               |

| HSTL-18 Class<br>I  | _               | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                      | V <sub>CCIO</sub> - 0.4  | 8                               | -8                              |

| HSTL-18 Class<br>II | _               | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                      | V <sub>CCIO</sub> - 0.4  | 16                              | -16                             |

| HSTL-15 Class<br>I  | _               | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                      | V <sub>CCIO</sub> - 0.4  | 8                               | -8                              |

| HSTL-15 Class<br>II | _               | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                      | V <sub>CCIO</sub> - 0.4  | 16                              | -16                             |

| HSTL-12 Class<br>I  | -0.15           | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | 0.25 × V <sub>CCIO</sub> | 0.75 × V <sub>CCIO</sub> | 8                               | -8                              |

| HSTL-12 Class<br>II | -0.15           | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | 0.25 × V <sub>CCIO</sub> | 0.75 × V <sub>CCIO</sub> | 16                              | -16                             |

| HSUL-12             | _               | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> - 0.22  | V <sub>REF</sub> + 0.22  | 0.1 × V <sub>CCIO</sub>  | 0.9 × V <sub>CCIO</sub>  | _                               | _                               |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

## **Differential SSTL I/O Standards**

Table 18. Differential SSTL I/O Standards for Cyclone V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>SWI</sub> | NG(DC) (V)              |                                 | <b>V</b> <sub>X(AC)</sub> <b>(V)</b> |                              | V <sub>SWING</sub>                            | (AC) (V)                                      |

|------------------------|-------|-----------------------|-------|------------------|-------------------------|---------------------------------|--------------------------------------|------------------------------|-----------------------------------------------|-----------------------------------------------|

|                        | Min   | Тур                   | Max   | Min              | Max                     | Min                             | Тур                                  | Max                          | Min                                           | Max                                           |

| SSTL-2 Class I,<br>II  | 2.375 | 2.5                   | 2.625 | 0.3              | V <sub>CCIO</sub> + 0.6 | V <sub>CCIO</sub> /2 - 0.2      | _                                    | V <sub>CCIO</sub> /2 + 0.2   | 0.62                                          | V <sub>CCIO</sub> + 0.6                       |

| SSTL-18 Class<br>I, II | 1.71  | 1.8                   | 1.89  | 0.25             | V <sub>CCIO</sub> + 0.6 | V <sub>CCIO</sub> /2 -<br>0.175 | _                                    | V <sub>CCIO</sub> /2 + 0.175 | 0.5                                           | V <sub>CCIO</sub> + 0.6                       |

| SSTL-15 Class<br>I, II | 1.425 | 1.5                   | 1.575 | 0.2              | (20)                    | V <sub>CCIO</sub> /2 - 0.15     | _                                    | V <sub>CCIO</sub> /2 + 0.15  | 2(V <sub>IH(AC)</sub> -<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> -<br>V <sub>REF</sub> ) |

| SSTL-135               | 1.283 | 1.35                  | 1.45  | 0.18             | (20)                    | V <sub>CCIO</sub> /2 - 0.15     | V <sub>CCIO</sub> /2                 | V <sub>CCIO</sub> /2 + 0.15  | 2(V <sub>IH(AC)</sub> -<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> - V <sub>REF</sub> )    |

| SSTL-125               | 1.19  | 1.25                  | 1.31  | 0.18             | (20)                    | V <sub>CCIO</sub> /2 - 0.15     | V <sub>CCIO</sub> /2                 | V <sub>CCIO</sub> /2 + 0.15  | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub> -<br>V <sub>REF</sub> ) |

## **Differential HSTL and HSUL I/O Standards**

Table 19. Differential HSTL and HSUL I/O Standards for Cyclone V Devices

| I/O Standard           | ١     | v <sub>ccio</sub> (v) |       | V <sub>DII</sub> | (DC) (V)                |                                   | <b>V</b> <sub>X(AC)</sub> ( <b>V</b> ) |                                   |                         | V <sub>CM(DC)</sub> (V) |                         | V <sub>DIF(</sub> | <sub>AC)</sub> (V)       |

|------------------------|-------|-----------------------|-------|------------------|-------------------------|-----------------------------------|----------------------------------------|-----------------------------------|-------------------------|-------------------------|-------------------------|-------------------|--------------------------|

|                        | Min   | Тур                   | Max   | Min              | Max                     | Min                               | Тур                                    | Max                               | Min                     | Тур                     | Max                     | Min               | Max                      |

| HSTL-18 Class<br>I, II | 1.71  | 1.8                   | 1.89  | 0.2              | _                       | 0.78                              | _                                      | 1.12                              | 0.78                    | _                       | 1.12                    | 0.4               | -                        |

| HSTL-15 Class<br>I, II | 1.425 | 1.5                   | 1.575 | 0.2              | _                       | 0.68                              | _                                      | 0.9                               | 0.68                    | _                       | 0.9                     | 0.4               | -                        |

| HSTL-12 Class<br>I, II | 1.14  | 1.2                   | 1.26  | 0.16             | V <sub>CCIO</sub> + 0.3 | _                                 | 0.5 × V <sub>CCIO</sub>                | _                                 | 0.4 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.6 × V <sub>CCIO</sub> | 0.3               | V <sub>CCIO</sub> + 0.48 |

| HSUL-12                | 1.14  | 1.2                   | 1.3   | 0.26             | 0.26                    | 0.5 × V <sub>CCIO</sub><br>- 0.12 | 0.5 × V <sub>CCIO</sub>                | 0.5 × V <sub>CCIO</sub><br>+ 0.12 | 0.4 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.6 × V <sub>CCIO</sub> | 0.44              | 0.44                     |

The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

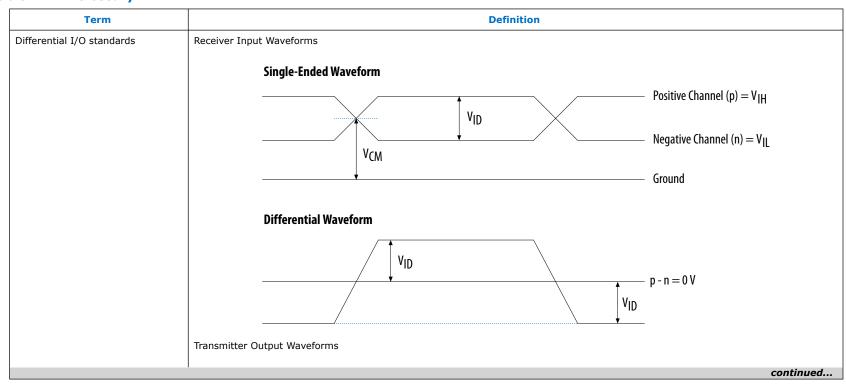

## **Differential I/O Standard Specifications**

#### Table 20. Differential I/O Standard Specifications for Cyclone V Devices

Differential inputs are powered by  $V_{\text{CCPD}}$  which requires 2.5 V.

| I/O Standard               | ,      | V <sub>CCIO</sub> (V) |       |     | V <sub>ID</sub> (mV) <sup>(21)</sup> |     |       | V <sub>ICM(DC)</sub> (V)       |       | V     | OD (V)(22 | !)  | Voc   | <sub>M</sub> (V) <sup>(22)</sup> | (23)     |

|----------------------------|--------|-----------------------|-------|-----|--------------------------------------|-----|-------|--------------------------------|-------|-------|-----------|-----|-------|----------------------------------|----------|

|                            | Min    | Тур                   | Max   | Min | Condition                            | Max | Min   | Condition                      | Max   | Min   | Тур       | Max | Min   | Тур                              | Max      |

| PCML                       | Transm | itter, rece           |       |     | ence clock pins<br>fications, refer  |     |       |                                |       |       |           |     |       | nd referen                       | ce clock |

| 2.5 V LVDS <sup>(24)</sup> | 2.375  | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05  | D <sub>MAX</sub> ≤ 700<br>Mbps | 1.80  | 0.247 | _         | 0.6 | 1.125 | 1.25                             | 1.375    |

|                            |        |                       |       |     |                                      |     | 1.05  | D <sub>MAX</sub> > 700<br>Mbps | 1.55  |       |           |     |       |                                  |          |

| BLVDS <sup>(25)(26)</sup>  | 2.375  | 2.5                   | 2.625 | 100 | _                                    | _   | -     | -                              | _     | _     | _         | _   | _     | -                                | -        |

| RSDS (HIO) <sup>(27)</sup> | 2.375  | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.25  | _                              | 1.45  | 0.1   | 0.2       | 0.6 | 0.5   | 1.2                              | 1.4      |

| Mini-LVDS (HIO)            | 2.375  | 2.5                   | 2.625 | 200 | _                                    | 600 | 0.300 | _                              | 1.425 | 0.25  | _         | 0.6 | 1     | 1.2                              | 1.4      |

|                            | •      | •                     | •     | •   |                                      |     | •     |                                |       |       |           | •   | •     | cont                             | nued     |

$<sup>^{(21)}</sup>$  The minimum  $V_{ID}$  value is applicable over the entire common mode range,  $V_{CM}$ .

- (27) For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- (28) For optimized mini-LVDS receiver performance, the receiver voltage input range must be within 0.300 V to 1.425 V.

<sup>&</sup>lt;sup>(22)</sup>  $R_L$  range:  $90 \le R_L \le 110 \Omega$ .

<sup>(23)</sup> This applies to default pre-emphasis setting only.

<sup>(24)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rate above 700 Mbps and 0.00 V to 1.85 V for data rate below 700 Mbps.

<sup>(25)</sup> There are no fixed  $V_{ICM}$ ,  $V_{OD}$ , and  $V_{OCM}$  specifications for BLVDS. They depend on the system topology.

<sup>(26)</sup> For more information about BLVDS interface support in Intel devices, refer to AN522: Implementing Bus LVDS Interface in Supported Intel Device Families.

| I/O Standard           | ,     | V <sub>CCIO</sub> (V) |       |     | V <sub>ID</sub> (mV) <sup>(21)</sup> |     |      | V <sub>ICM(DC)</sub> (V)       |      | V   | OD (V)(22 | 2)  | Voc | <sub>M</sub> (V) <sup>(22)</sup> | (23) |

|------------------------|-------|-----------------------|-------|-----|--------------------------------------|-----|------|--------------------------------|------|-----|-----------|-----|-----|----------------------------------|------|

|                        | Min   | Тур                   | Max   | Min | Condition                            | Max | Min  | Condition                      | Max  | Min | Тур       | Max | Min | Тур                              | Max  |

| LVPECL <sup>(29)</sup> | _     | _                     | _     | 300 | _                                    | _   | 0.60 | D <sub>MAX</sub> ≤ 700<br>Mbps | 1.80 | _   | _         | _   | _   | _                                | _    |

|                        |       |                       |       |     |                                      |     | 1.00 | D <sub>MAX</sub> > 700<br>Mbps | 1.60 |     |           |     |     |                                  |      |

| SLVS                   | 2.375 | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05 | _                              | 1.80 | _   | _         | _   | _   | _                                | _    |

| Sub-LVDS               | 2.375 | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05 | _                              | 1.80 | _   | _         | _   | _   | _                                | _    |

| HiSpi                  | 2.375 | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05 | _                              | 1.80 | _   | _         | _   | _   | _                                | _    |

#### **Related Information**

- AN522: Implementing Bus LVDS Interface in Supported Intel Device Families

Provides more information about BLVDS interface support in Intel devices.

- Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices on page 25 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

# **Switching Characteristics**

This section provides performance characteristics of Cyclone V core and periphery blocks.

$<sup>^{(21)}\,</sup>$  The minimum  $V_{ID}$  value is applicable over the entire common mode range,  $V_{CM}.$

<sup>(22)</sup>  $R_1$  range:  $90 \le R_1 \le 110 Ω$ .

<sup>(23)</sup> This applies to default pre-emphasis setting only.

<sup>(29)</sup> For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rate above 700 Mbps and 0.45 V to 1.95 V for data rate below 700 Mbps.

# **Transceiver Performance Specifications**

# Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices

Table 21. Reference Clock Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description                                     | Condition                                                | Transceiv | er Speed G     | rade 5 <sup>(30)</sup> | Transce      | iver Speed     | Grade 6                   | Transce     | iver Speed     | Grade 7 | Unit    |

|--------------------------------------------------------|----------------------------------------------------------|-----------|----------------|------------------------|--------------|----------------|---------------------------|-------------|----------------|---------|---------|

|                                                        |                                                          | Min       | Тур            | Max                    | Min          | Тур            | Max                       | Min         | Тур            | Max     |         |

| Supported I/O standards                                |                                                          | 1.2       | 2 V PCML, 1.   | 5 V PCML, 2.           | .5 V PCML, [ | Differential L | VPECL <sup>(31)</sup> , H | CSL, and LV | DS             |         | •       |

| Input frequency from REFCLK input pins <sup>(32)</sup> | _                                                        | 27        | _              | 550                    | 27           | _              | 550                       | 27          | _              | 550     | MHz     |

| Rise time                                              | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | _              | 400                    | _            | _              | 400                       | _           | _              | 400     | ps      |

| Fall time                                              | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | _              | 400                    | _            | _              | 400                       | _           | _              | 400     | ps      |

| Duty cycle                                             | _                                                        | 45        | _              | 55                     | 45           | _              | 55                        | 45          | _              | 55      | %       |

| Peak-to-peak differential input voltage                | _                                                        | 200       |                | 2000                   | 200          | _              | 2000                      | 200         | _              | 2000    | mV      |

| Spread-spectrum<br>modulating clock frequency          | PCIe                                                     | 30        | _              | 33                     | 30           | _              | 33                        | 30          | _              | 33      | kHz     |

| Spread-spectrum<br>downspread                          | PCIe                                                     | _         | 0 to -<br>0.5% | _                      | _            | 0 to -<br>0.5% | _                         | _           | 0 to -<br>0.5% | _       | _       |

| On-chip termination resistors                          | _                                                        | _         | 100            | _                      | _            | 100            | _                         | _           | 100            | _       | Ω       |

|                                                        | •                                                        | •         |                |                        |              | •              |                           | •           |                | co      | ntinued |

<sup>(30)</sup> Transceiver Speed Grade 5 covers specifications for Cyclone V GT and ST devices.

$<sup>^{(33)}</sup>$  REFCLK performance requires to meet transmitter REFCLK phase noise specification.

<sup>(31)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.